# Panel Level \_ Device Embedded Module

## [背景]

狭ピッチ、多ピンのFun-out CSPを基板サイズレベルで製造するパッケージング技術が注目を集めている。 三次元半導体研究センターでは、部品内蔵技術を用いて、コア基板のキャビティ内にICチップ、受動部品を 内蔵する基板レベル部品内蔵モジュール(Panel Level \_ Device Embedded Module)の構造設計、プロセス開発 を行っている。

## [設計概要]

#### パッケージ基本仕様

- 1.型番:SIPOS PL DEM0201

- 2.基板構成: 2-2-2ビルドアップ基板

- \*コアキャビティにChip及びキャパシタを内蔵

- 3.PKGサイズ: 16.0mm×16.0mm×t0.4~0.5 mm

- 4.基板搭載面端子数

- **①PL\_DEM0201\_01:79Pad(Fan-out)**

- **②PL\_DEM0201\_02:143Pad(Full-Array)**

- ③PL\_DEM0201\_03:95pad(Fan-in + Fan-out)

- 5. 塔載部品

- 5-1.TEG-Chip

- -型名: STAC-0101JY(WALTS社製)

- · 搭載チップサイズ: 9.0mm×9.0mm×t0.2 mm

- •Padピッチ: 120µm

- -Pad表面: Cuポスト(ポスト高:20μm, φ100μm)

- 5-2.キャパシタ 12個/1PKG 搭載

- ・サイズ: 1.0mm×0.5mm×t0.18mm

- ・電極表面: Cuめっき

### STAC TEG(9mm × 9mm) キャパシタ(1.0mm×0.5mm) 9 x 9 mm size die including $A \sim H$ piezo-resistor Die pad & bump structure 16.0mm 株式会社WALTS殿ご提供 PL DEM0201 モジュール外形 内蔵した応力評価チップ(STAC-TEG) 外部端子(Ni/Au) ソルダレジスト **◢**層間材料 -コア基板 STAC-TEG Chip

PL\_DEM0201断面概略図

## 【試作評価結果】

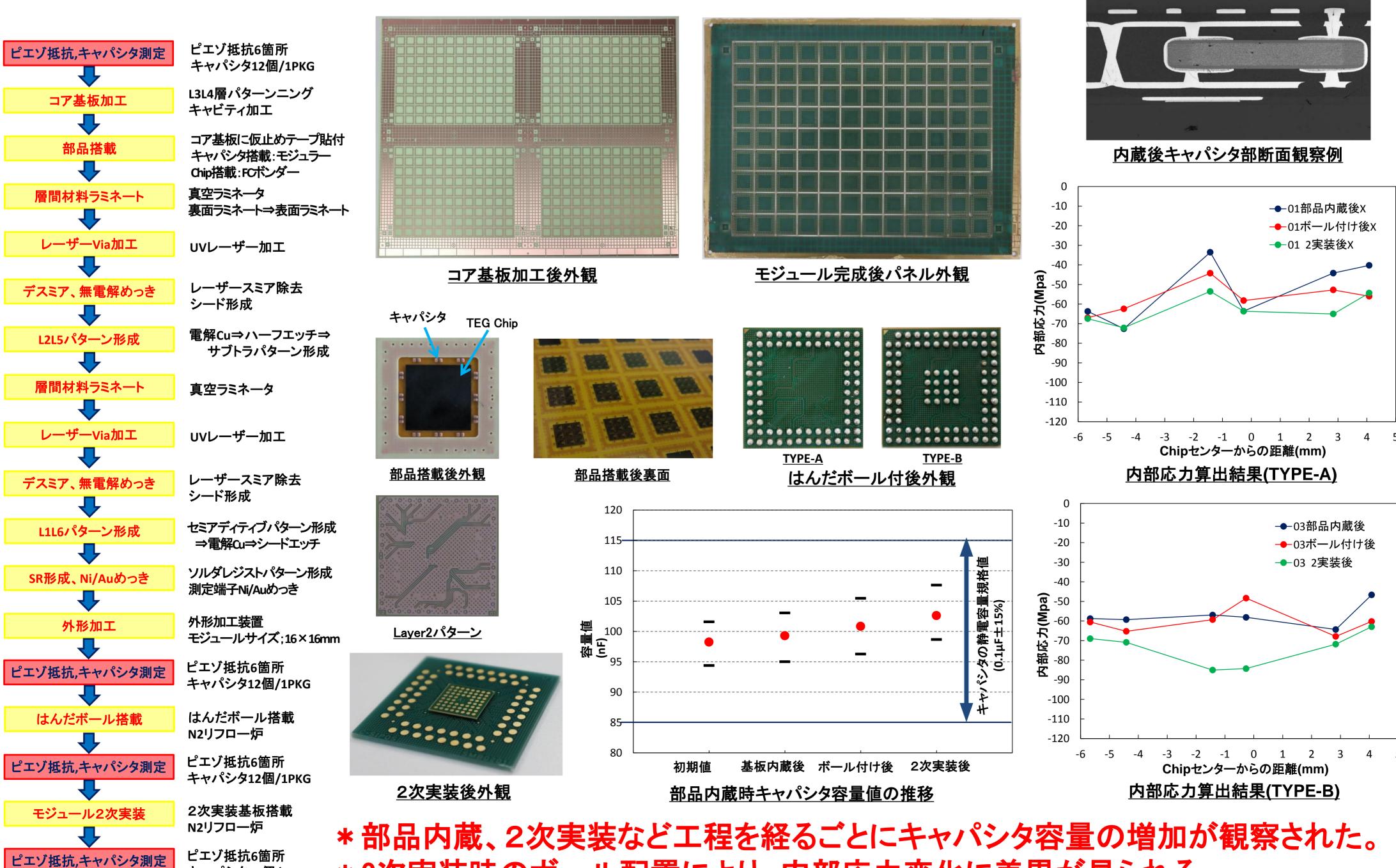

PL DEM0201製造プロセス及び評価フロー

- キャパシタ12個/1PKG

- \*2次実装時のボール配置により、内部応力変化に差異が見られる。