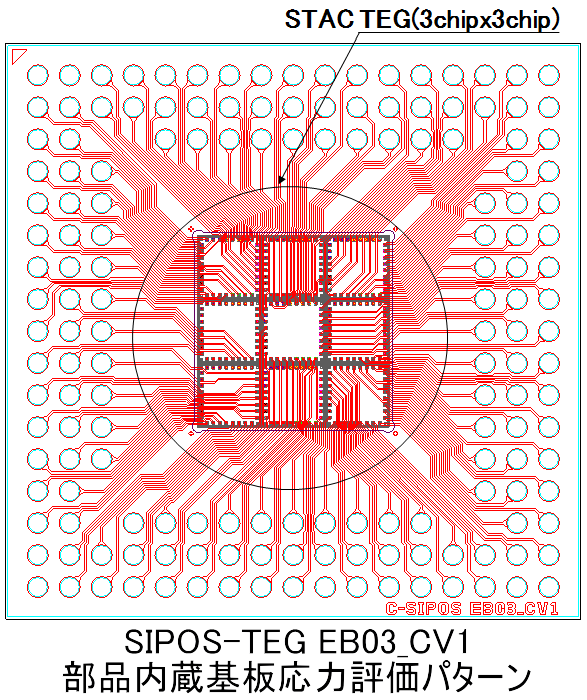

福岡大学共同開発 SIPOS-TEG EB03_CV1

部品内蔵基板の構造、及び構成材料により発生する、内蔵チップ内部の応力を評価する

評価TEGと基本製造条件を使った試作・評価が可能

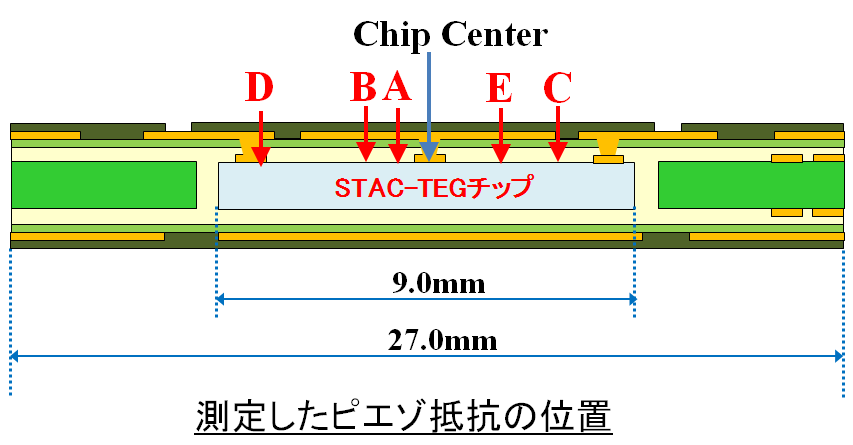

応力評価TEGキャビティ内蔵基板仕様

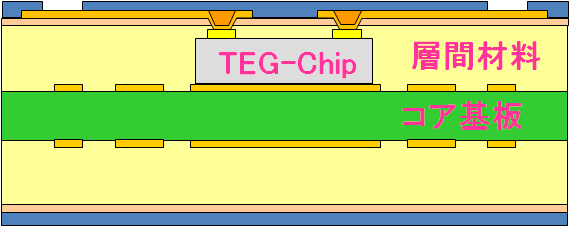

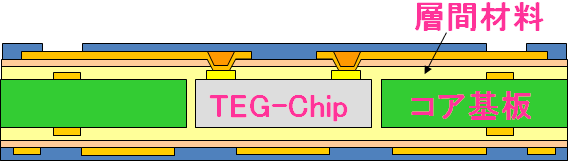

1.基板構成:1-2-1ビルドアップ基板(コア内に部品内蔵)

2.層構成

①Layer1 Viaランド、表層配線、測定端子

②Layer2 キャビティ、内層配線、TH

③Layer3 キャビティ、内層配線、TH

④Layer4 裏面配線、測定端子、Viaランド

⑤Via1 Layer1-Pad間

⑥Via2 Layer1-Layer2間接続

⑦Via3 Layer4-Chip裏面間接続

⑧Via4 Layer4-部品端子間

⑨TH Layer2-Layer3間接続

⑩SR1 表面ソルダレジスト

⑪SR2 裏面ソルダレジスト

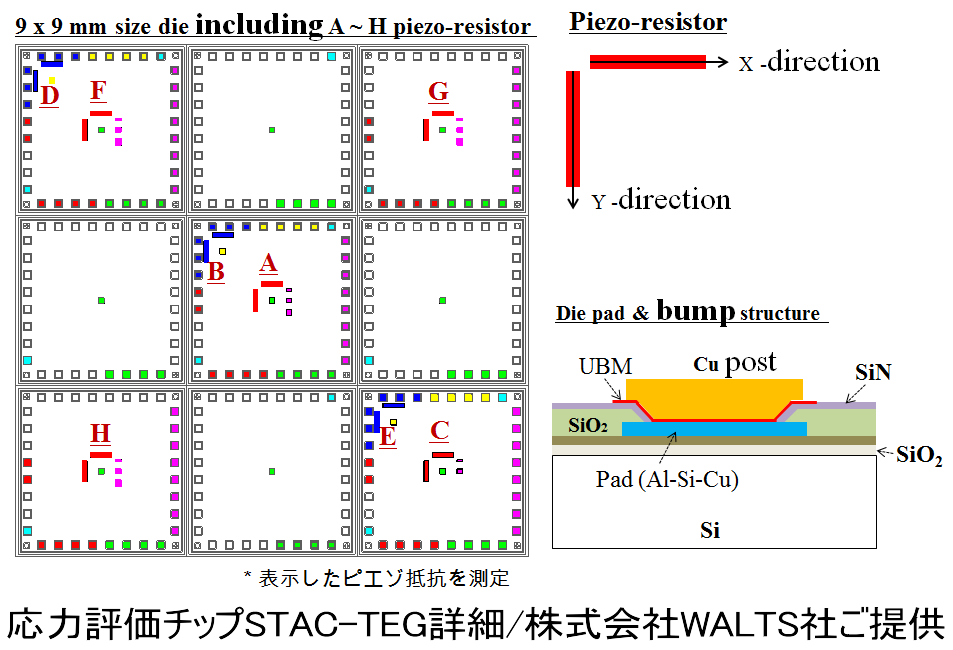

3.塔載チップ

・型名: STAC-0101JY(WALTS社製)

・搭載チップサイズ:9.0mm×9.0mm×t0.2 mm

(ベースチップを3x3で使用)

・Padピッチ:120μm

・Pad表面:Cuポスト(ポスト高:20μm , φ100μm)

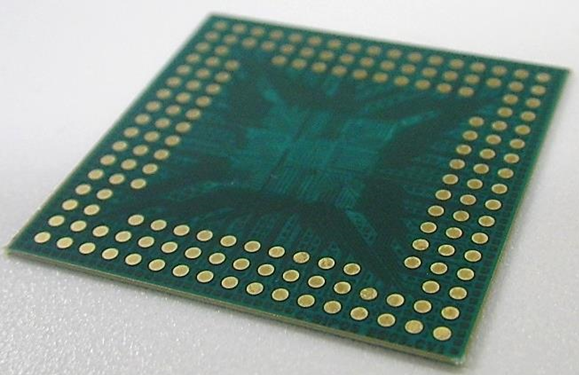

4.基板サイズ

・フレームサイズ:94mmx74mm

・個片サイズ:27mmx27mm

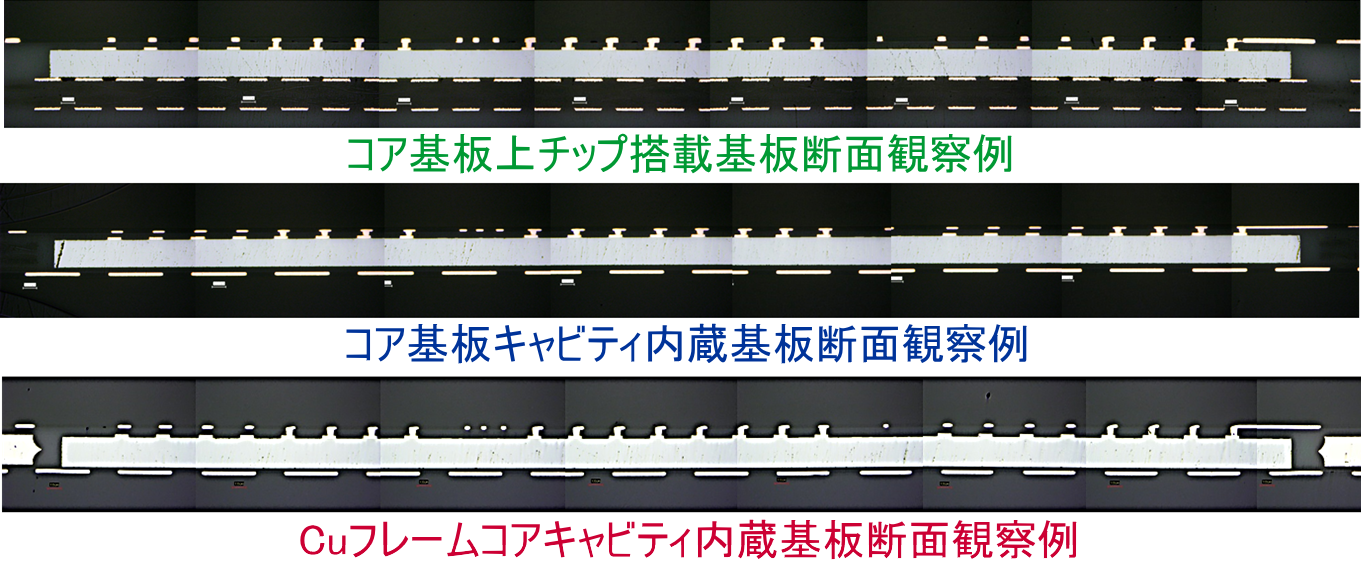

評価構造例

|

|

|

|---|---|---|

| コア基板上チップ搭載 |

コア基板キャビティ内蔵 |

Cuフレームコアキャビティ内蔵 |

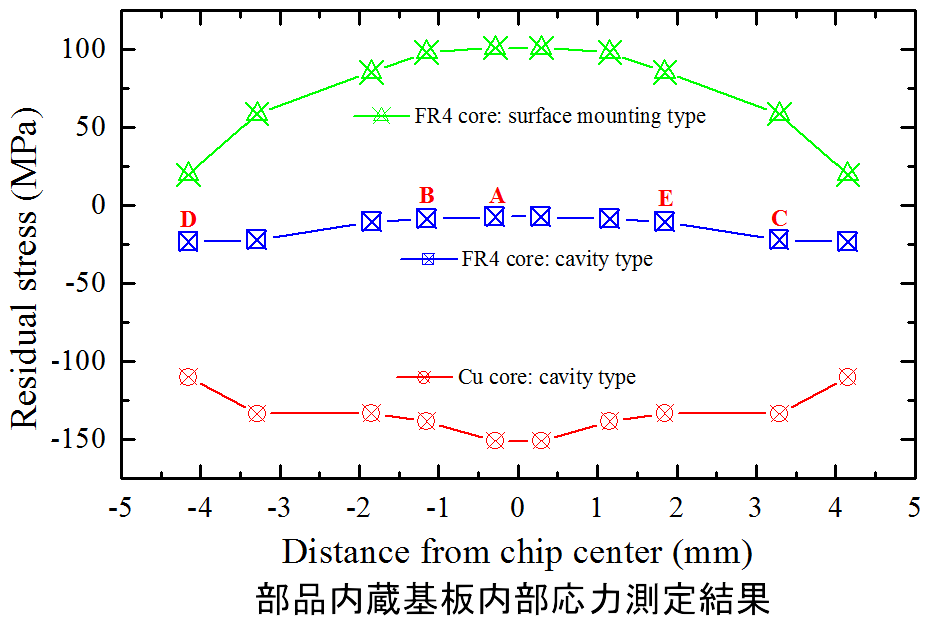

応力測定結果例

基板構造、構成材料により内部応力に大きな差があることが判明